기존에 있던 회로를 분석해가며 공부를 하고 있습니다!!!!

MAX 45V의 입력을 받아 24V의 베터리를 출전하는 회로인데...어떤식으로 FET의 G를 조절하는지를 모르겠습니다..ㅠㅠ

FET의 Vgs(th) = -2 ~ -4V 의 P-Channel FET인데...

스위칭 작용을 하기 위해선 Vgg 가 Vss보다 -2 ~ -4V 정도 차이가 나야하는거 맞는지요??

스위칭을 위해 PWM제어를 위해 MCU를 사용하지만 턱없이 부족한 전압으로 인해 BJT를 사용했다 생각되는데..맞는걸까요..??

회로가 돌아가는 순서?? 그런것도 하나도 이해가 안되고..ㅠㅠ

요 회로가 심각한 두통을 초래하며, 일상생활에 지장을 미치고 있습니다..ㅠㅠ

제너는 머때문에 썼는지도 모르겠고...ㅠㅠ

결혼식도 앞두고 있는데...이거때문에 신경을 하나도 못쓰겠네요..ㅠㅠ

부디 자비를 배풀어 빈민을 구제해 주셨으면 합니다..으하~ㅠㅠ

제발 도와주세요!!ㅠㅠ

또한 위 회로를 응용하여 이전 질문(Buck-Converter)을 합쳐서, 제너와 2k저항, TR등을 활용하여 MCU의 PWM을 사용하여, Buck_Converter 를 만들려고 하고 있습니다. 회로를 꾸미고(회로 이해가 다 되는건 아니지만...결과라도 나오면 좋을꺼 같아서...ㅠㅠ) 돌렸는데...결과가 안나오네요...//

인덕터 입력전류도 변화가 없고....흐아...어떻게 회로를 꾸미면 꾸밀수록..더욱더...어려워 지는걸까요..??

또다시 글올리기가 죄송스러워...질문에대한 답변으로 추가 질문을 드립니다...ㅠㅠ

<답변>정말 상세한 답변 감사드립니다!!ㅎㅎ 염치없지만 좀더 상세한 설명을 부탁 드려도 될런지요??

1. Battery와 MAX 45V의 위치를 바꿔야 회로가 구성 된다고 하셨는데... FET의 방향을 바꾸어도 상관 없는지요..??

=>fet방향을 바꾸라는 것이 아니라 회로가 바뀌는 겁니다.

현재 회로에서 입력이 좌우로 바뀌면 됩니다.

<<질문>>D G S 인데 이것을 좌우 대칭으로 돌려서 S G D 으로 바꿔만 줘서 회로가 구성이 될까요..??아니면 P-Channel을 N-Channel로 바꿔야 하는지..?? P.S) 위 회로도의 일부이지만 Battery쪽 역시 그림과 같은 회로가 되어 있습니다. MAX 45V -> P-Channel FET(D-G-S) -> P-Channel FET(S-G-D) -> Battery(24V) 각 P-Channel FET에는 제너, 2k, 510, TR등의 단자가 똑같이 연결되어 있는 상황입니다. 당연히 PWM은 따로 조절이되고 있습니다..ㅎㅎ 이런상황이라면 입력단과 출력단은 바꾸지 않더라도 상관은 없는거겠지요?? Body-Diode를 통해 Battery로 들어가는것을 Battey쪽 FET에서 막아주니 말입니다. 2. 제너, 2K, 510, RT 등이 입력전원 쪽으로 붙어야 제대로 동작을 하는건지요..??

=>제 생각에는 제너 2k,510이 입력쪽에 붙어서 pwm신호를 기다려야 한다고 봅니다.

pspice 회로를 보면 제너가 출력에 연결되어 있는데? fet가 동작을 하나요?

그래서 제너회로가 입력에 연결되어서 fet동작 조건을 먼저 만들어 준 다음 pwm해야 합니다.

아마 <뒷동산쓰레귀>는 시험이 끝났을 것 같습니다.ㅎㅎㅎ

<<질문>>또한 위 회로를 응용하여 이전 질문(Buck-Converter)을 합쳐서, 제너와 2k저항, TR등을 활용하여 MCU의 PWM을 사용하여, Buck_Converter 를 만들려고 하고 있습니다. 회로를 꾸미고(회로 이해가 다 되는건 아니지만...결과라도 나오면 좋을꺼 같아서...ㅠㅠ) 돌렸는데...결과가 안나오네요...//

인덕터 입력전류도 변화가 없고....흐아...어떻게 회로를 꾸미면 꾸밀수록..더욱더...어려워 지는걸까요..??

또다시 글올리기가 죄송스러워...질문에대한 답변으로 추가 질문을 드립니다...ㅠㅠ

=>저도 잘은 모르지만, 질문을 열심히?하셔서,저도 공부하고 있습니다.ㅎㅎ

pwm하면 버크컨버터를 떠올리게 됩니다.그만큼 유명하긴 하죠?

전 지금도 버크콘버터가 스윗칭파워의 기본이지 않나 생각하고 있는 사람입니다.

버크콘버터에 사용되는 스윗치,즉 on/off를 할 수 있는 소자가 fet,혹은 tr인데..요즈음은 fet를 선호합니다.

fet는 p-ch,n-ch를 둘다 사용할 수 있으며,회로에 따라 p-ch를 사용하기도 하고 n-ch를 사용하기도 합니다.

그런데,실재로 사용되는 것은 p-ch보다는 n-ch가 많습니다.(단가가 p-ch>>n-ch),

그래서 가능하면 가격이 싼 n-ch fet를 사용하고 있습니다.(또한 많이 사용하면 가격이 당연히 떨어집니다.ㅎㅎ)

그런데 위 회로에서는 n-ch fet를 사용하기기 조금은 어렵습니다.게이트 동작전압 만들기가 조금은 힘듬.ㅠㅠ

그래서 쫌~비싸지만 p-ch fet를 사용합니다.

물론 n-ch fet를 사용하기 위해 게이트 드라이브회로를 추가해도 됩니다.(조금 돈이 듭니다~)

p-ch를 사용하던,n-ch를 사용하던 설계자 맘이지만,회로 복잡도와 단가는 확실히 차이가 납니다.

감사합니다.

근데 결혼은 언제 하남요?ㅎㅎ

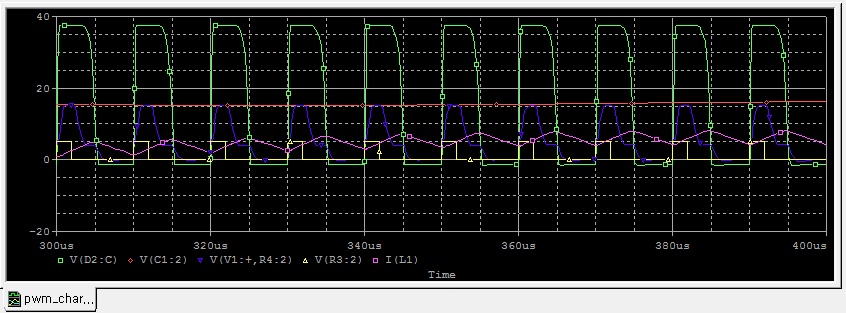

1)r4=100옴,r5=100시 파형입니다.

2)r4=10옴,r5=10시 파형입니다.

r4와 r5변경이유

위 회로가 단순이 on/off만 하는 회로라면 스위칭 속도가 별로 크게 영향을 주지 않습니다.

r4=r5=100 와 r4=r5=10이 다른 이유는 fet의 게이트 저항및 fet의 gate charge의 방전시간 때문에 100-100옴에서는

입력과 출력 파형이 상당히 다른 파형(delay)이 됩니다.

스윗칭회로에 사용되는 fet를 설계시 게이트회로에 많은 실험을 해야하고 또한 노하우도 있습니다.

게이트저항을 무작정 작게 한다고 좋아지지 않으며,스위칭속도가 빨라지면 회로노이즈가 증가하기도 합니다.열이 감소하기도 하죠~

게이트저항이 넘 크면 스위칭속도가 느려져서 위와 같은 현상이 나타나고..부가적으로 열이 증가할 수도 있습니다.

이럴땐 회로 노이즈가 감소하는 경향이 있습니다.

여러가지를 고려한 tradeoff를 해야 합니다.

심뮬레이션이 도움이 되길 바랍니다.

감사합니다.

PS>pn2222는 전류용량을 3A로 올려서 시험했습니다.

(적절한 라이브러리 찾기가 귀찮아서.ㅎㅎ)